基于DSP的混合信号解决方案解决高级音频处理难题

从20世纪70年代产生构想以来,特别是在过去十年间,数据信号处理(DSP)在媒体应用激增的推动下,已经成为了一项耳熟能详的技术。从用于军事的语音和图像处理开始,这项技术首先发展进入音频和视频的应用环境,随即又进入了更加主流的电子领域。

今天,设计师们正面临着如下一系列信号处理方面的挑战:要求同时具备先进的功能性、便携性和低耗能性的应用,其要求不断增加。音频领域是个典型应用:从专业耳机到电子听诊器和遥感器,新的应用不断出现,这就要求工程师利用电池供电,以相对较低的成本和小型化设计实现音频压缩和录音、声音管理、回波消除和言语处理。

但是应用的便携性增加了这些挑战的难度:低能耗不仅仅要求提高电池寿命,还要求降低电池的尺寸大小和重量。尺寸限制还要求组件数量越少越好,而设备的复杂性则不断随着市场要求产品所具特色的增加而增加。最后,市场的快速变化向设计师们施压,他们必须比以前更加迅速地完成项目,并尽快将他们的想法转化成销售额。因此,IP复用或某些形式的可编程性至关重要。

有充分证据证明,实现信号处理功能集成的驱动力也对传统上模拟和数字电子技术之间的分离造成了冲击,使得混合信号的IC设计更加普遍。对于芯片设计师来说,这本身就困难重重:例如,他们需要设计具备多重地和电源的组件,并确保模拟和数字两部分之间的充分隔离,因为其中一部分可能干扰到另一部分。

尽管存在这些固有的难题,系统设计师的需求已经使模拟和数字技术集成于芯片上变得不可避免。产业从许多不同的方向解决了这个问题:线性电路的制造商已经开始向他们的设备添加数字功能;同时可编程逻辑技术的供应商也已经尝试集成模拟功能。但是,最重要和最成功的事情可能是,微处理器、DSP以及DSP核心的制造商一直努力在芯片上集成更多外围功能。今天,具有真正专门知识和处理技术的设备供应商可以提供具备ADC、DAC、显示驱动器、电源管理、集成放大器以及许多在特殊应用中普遍使用的外围支持功能的单芯片信号处理解决方案。

单芯片音频处理解决方案

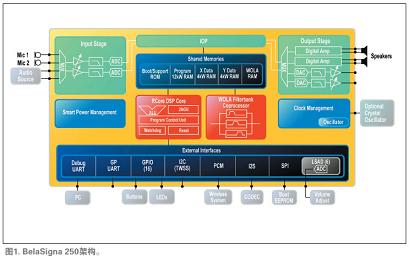

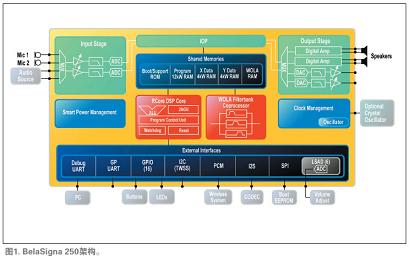

图1展示了由AMI半导体公司开发的经优化的混合信号片上系统音频处理解决方案的示意图。这款被称为BelaSigna™ 250的芯片提供了一个极好的例子,证明了当前使用最新的混合信号半导体处理技术而可能达到的集成水平。

该设备以将非同寻常的功率效率与高性能有机结合的平行处理架构为基础,构成了一个完整的音频解决方案,包括ADC与DAC、滤波器、放大器和电源管理电路。使用一个完全可编程的16位定点双哈佛架构DSP核心作为其主处理器,意味着BelaSigna 250可以迅速地在软件中进行配置——利用AMIS或第三方软件合作伙伴提供的程序库功能,使这个进程得以加速。

通过纳入加权叠加式(WOLA)滤波器组协处理器而引入的平行性,通过在时间域和频率域之间的一个信号上进行转换以及其它基于矢量的计算,推动了数字滤波。这个硬件加速功能使得在便携式设计中所要求的电源效率和空间要求成为可能。

这个平行处理器架构被一个完全立体声的音频信号链所环绕,包括经由16位过采样∑-△A/D转换器的输入和包括模拟线路输出以及可以直接驱动扩音器的差分数字功率输出。音频链杰出的保真度提供了一个88dB的整体系统动态范围。架构能够执行双精度 *** 作意味着这个信号保真度可以在处理期间被维持。通过在WOLA滤波器组协处理器中使用的新时间—频率转换算法,实现了极低的系统噪音以及较低的群延迟。

由经过音频优化的DMA单元,即输入/输出处理器(IOP)来管理设备内的信号数据。这个单元管理着从ADC和输入FIFO得来的数据集合。在处理之后,它还向音频输出级和输出FIFO馈送数字数据。每一个FIFO本身具备两个内部接口:其一是一个标准顺序,当数据到达时,最近输入块的地址会发生改变;其二是一个用于时域滤波的“智能”接口,最近的输入在那里保持不变。

除了接口连接的灵活性之外,可以通过四种一般意义上有所不同的方法来访问FIFO中的数据:单声道模式;简单立体声模式;数字混合模式;以及完全立体声模式。这些模式为立体声数据以及单声道/立体声输入/输出配置的交叉或分块存储提供了多样的选择。

通过在一个单独设备中合并两个主要的处理单元、硬件加速、数据管理以及输入/输出信号调节,设计师可以更快更简单地集成更大的系统。他们可以显著地削减组件数量,满足便携式装备中固有的小尺寸要求。加入I2S、PCM、SPI、I2C、TWSS和GPIO的直接接口,以及采用设备的小型形状因子(64针脚LFBGA包,尺寸仅为7mmx7mm)和处理数据的集成IOP,进一步帮助设计师实现小型化。

此外,BelaSigna 250还加入了许多额外功能,有助于降低功耗。该设备具有低功耗设计。例如,系统在平均负载下以1.8V的供电电压和20MHz的时钟频率工作,通常将消耗不到5mA的电量。为了额外节能,每一个输入通道都可以通过软件关断,同时,仅需0.05mA电流供应的低电流待机模式延长了电池寿命。

从20世纪70年代产生构想以来,特别是在过去十年间,数据信号处理(DSP)在媒体应用激增的推动下,已经成为了一项耳熟能详的技术。从用于军事的语音和图像处理开始,这项技术首先发展进入音频和视频的应用环境,随即又进入了更加主流的电子领域。

今天,设计师们正面临着如下一系列信号处理方面的挑战:要求同时具备先进的功能性、便携性和低耗能性的应用,其要求不断增加。音频领域是个典型应用:从专业耳机到电子听诊器和遥感器,新的应用不断出现,这就要求工程师利用电池供电,以相对较低的成本和小型化设计实现音频压缩和录音、声音管理、回波消除和言语处理。

但是应用的便携性增加了这些挑战的难度:低能耗不仅仅要求提高电池寿命,还要求降低电池的尺寸大小和重量。尺寸限制还要求组件数量越少越好,而设备的复杂性则不断随着市场要求产品所具特色的增加而增加。最后,市场的快速变化向设计师们施压,他们必须比以前更加迅速地完成项目,并尽快将他们的想法转化成销售额。因此,IP复用或某些形式的可编程性至关重要。

有充分证据证明,实现信号处理功能集成的驱动力也对传统上模拟和数字电子技术之间的分离造成了冲击,使得混合信号的IC设计更加普遍。对于芯片设计师来说,这本身就困难重重:例如,他们需要设计具备多重地和电源的组件,并确保模拟和数字两部分之间的充分隔离,因为其中一部分可能干扰到另一部分。

尽管存在这些固有的难题,系统设计师的需求已经使模拟和数字技术集成于芯片上变得不可避免。产业从许多不同的方向解决了这个问题:线性电路的制造商已经开始向他们的设备添加数字功能;同时可编程逻辑技术的供应商也已经尝试集成模拟功能。但是,最重要和最成功的事情可能是,微处理器、DSP以及DSP核心的制造商一直努力在芯片上集成更多外围功能。今天,具有真正专门知识和处理技术的设备供应商可以提供具备ADC、DAC、显示驱动器、电源管理、集成放大器以及许多在特殊应用中普遍使用的外围支持功能的单芯片信号处理解决方案。

单芯片音频处理解决方案

图1展示了由AMI半导体公司开发的经优化的混合信号片上系统音频处理解决方案的示意图。这款被称为BelaSigna™ 250的芯片提供了一个极好的例子,证明了当前使用最新的混合信号半导体处理技术而可能达到的集成水平。

该设备以将非同寻常的功率效率与高性能有机结合的平行处理架构为基础,构成了一个完整的音频解决方案,包括ADC与DAC、滤波器、放大器和电源管理电路。使用一个完全可编程的16位定点双哈佛架构DSP核心作为其主处理器,意味着BelaSigna 250可以迅速地在软件中进行配置——利用AMIS或第三方软件合作伙伴提供的程序库功能,使这个进程得以加速。

通过纳入加权叠加式(WOLA)滤波器组协处理器而引入的平行性,通过在时间域和频率域之间的一个信号上进行转换以及其它基于矢量的计算,推动了数字滤波。这个硬件加速功能使得在便携式设计中所要求的电源效率和空间要求成为可能。

这个平行处理器架构被一个完全立体声的音频信号链所环绕,包括经由16位过采样∑-△A/D转换器的输入和包括模拟线路输出以及可以直接驱动扩音器的差分数字功率输出。音频链杰出的保真度提供了一个88dB的整体系统动态范围。架构能够执行双精度 *** 作意味着这个信号保真度可以在处理期间被维持。通过在WOLA滤波器组协处理器中使用的新时间—频率转换算法,实现了极低的系统噪音以及较低的群延迟。

由经过音频优化的DMA单元,即输入/输出处理器(IOP)来管理设备内的信号数据。这个单元管理着从ADC和输入FIFO得来的数据集合。在处理之后,它还向音频输出级和输出FIFO馈送数字数据。每一个FIFO本身具备两个内部接口:其一是一个标准顺序,当数据到达时,最近输入块的地址会发生改变;其二是一个用于时域滤波的“智能”接口,最近的输入在那里保持不变。

除了接口连接的灵活性之外,可以通过四种一般意义上有所不同的方法来访问FIFO中的数据:单声道模式;简单立体声模式;数字混合模式;以及完全立体声模式。这些模式为立体声数据以及单声道/立体声输入/输出配置的交叉或分块存储提供了多样的选择。

通过在一个单独设备中合并两个主要的处理单元、硬件加速、数据管理以及输入/输出信号调节,设计师可以更快更简单地集成更大的系统。他们可以显著地削减组件数量,满足便携式装备中固有的小尺寸要求。加入I2S、PCM、SPI、I2C、TWSS和GPIO的直接接口,以及采用设备的小型形状因子(64针脚LFBGA包,尺寸仅为7mmx7mm)和处理数据的集成IOP,进一步帮助设计师实现小型化。

此外,BelaSigna 250还加入了许多额外功能,有助于降低功耗。该设备具有低功耗设计。例如,系统在平均负载下以1.8V的供电电压和20MHz的时钟频率工作,通常将消耗不到5mA的电量。为了额外节能,每一个输入通道都可以通过软件关断,同时,仅需0.05mA电流供应的低电流待机模式延长了电池寿命。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)