现在,芯片制造商在14/16nmFinfet制程的竞争进入了白热化阶段,而下一阶段的10nm和7nm的角逐也进入了预热阶段。与此同时,业界也正在推动工艺制程走向5nm。

TSMC表示,他们希望在2020年推出其5nm的工艺,而三星、格罗方德和英特尔也都在这个节点上投入了大量的金钱进行研发。

但我们可以明确知道的是,在5nm的时候,芯片制造商会面临很多未知的挑战。最基本的一点,我们连5nm真正到来时间和具体规格都没能确定。更不用说可能面对的技术和经济方面的挑战。退一万步,就算5nm真的确定下来,按照目前的演进,最终也就是只有几家公司能够承担起5nm制程的高昂费用。

“我目前的想法是5nm是会实现,但是直到2020年前,我们都不会看到大批量的投产”,Gartner的分析师Bob Johnson表示。如果你问我真正的量产时间,我觉得这个时间会是2021或者20222年,Bob补充说。

根据Bob的观点,设计一个可用的5nm SoC的成本会达到5亿美元,对比于7nm SoC的2.71亿美元,成本基本翻了一番。

和28nm 的平面型器件相比,更是天价,前者的价格是后者的9倍。

对于那些想把制程推进到5nm的企业来说,他们只有两个选择,一个是FinFet,另一个是横向的gate-all-around FET。

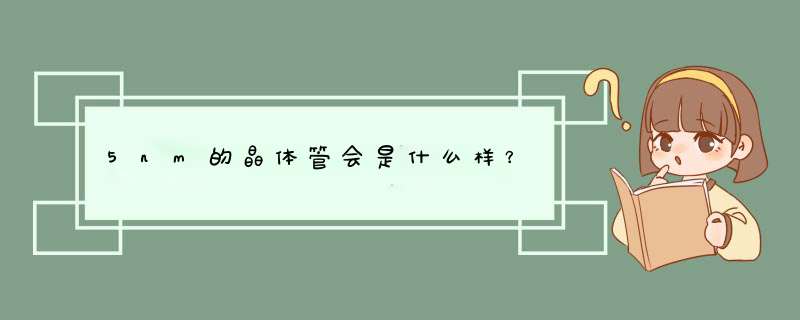

Gate-all-around (GAA),有时候被称作横向纳米线场效应管。这是一个周边环绕着gate的FinFet。

实际上,业界也围绕GAA上做了很多功夫。

按照Intel架构和集成方面的资深Fellow Mark Bohr的观点,GAA晶体管能够提供比FinFet更好的静电特性,这个可满足某些栅极宽度的需求。

但业界关于GAA的讨论还没有定性,因为还有些厂商考虑在5nm的时候使用FinFET。

除了架构之外,5nm还要面临的一个挑战就是市场的容量问题。5nm的投资回报比也是业界顾虑的一个因素。Bobr方面认为, 5nm的世代是会出现,且会覆盖很多类型的产品。

就目前情况看来,尽管Fab厂面临的挑战比较多,但GAA引起的争议还是比较大的。因为它会给patterns, gates, 纳米线和内部连接带来极大的挑战。除此之外,制程控制对晶圆厂来说也是一个噩梦。当然,如何平衡GAA Fet的成本也是很关键的。

为了帮助业界了解更多关于GAA Fet的细节,我们特意带大家去了解一下这个基本的制程流程和这个技术将会面临的挑战。另外,我们还会带大家去关注以下未来的设备,例如omplementaryFETs和垂直纳米线。

Gate-all-around是什么?

现在的业界在FinFet上的竞争已经进入了白热化阶段,但是他们当中没有一个能够取得领先位置。

例如在逻辑器件里面,其甜蜜节点依然是40nm和28nm这两个平面节点。

很多晶圆厂最近在28nm的营收表现甚至出现了很大幅度的攀升,尤其是在通信那块。UMC的CEO颜博文表示。在UMC最近的一个电话会议里面,他提到UMC的28nm产线的使用率在2016年第三季度上升到90%,较前一季度的70%有了很大的提升,他补充说。

高端市场持续升温。

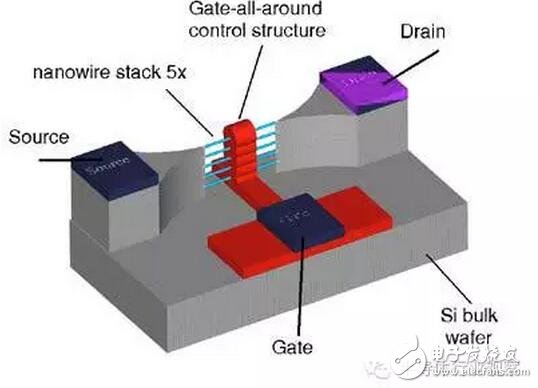

制程从22nm到16nm/14nm演变的过程中,芯片制造商的晶体管从平面型进化到FinFet,其中最大的一个原因就是FinFet可以解决平面型设备的短沟道问题。在FinFet的时候,通过在Fin的三面环绕gate,可以达到很好的控制电流的效果。最后,FinFET终于走进了主流。

三星的晶圆市场高级经理Kelvin Low表示,在7nm前,我们已经看到了挑战。我们倾向于在缩小CPP的时候提高Vcc(工作电压),但我们认为我们在7nm的CPP尺寸面临了很大的挑战。因此我们认为这需要不一样的设备结构和不同的技术去满足这种需求。

此外,内部铜导线在现在的节点变得越来越紧凑,这就提高了芯片的RC延迟,我们希望RC延迟得到很好的盖上,Low表示。

根据主流的观点,他们认为FinFet是可以扩展到5nm的,虽然这需要一些新的沟道材料的支持,例如为 pMOS注入SiGe。

应用材料的策略规划主管Mike Chudzik表示,这样做可以不但可以让你获得想要的性能,还不需要缩小fin的高度。但实际上,这样做是不允许你去缩小的栅极长度,但改善了移动性。

一旦fin的宽度到了5nm,FinFet就会失去动力。

“你可以缩小你的fin,但你会发现,你会受到量子限制,在你的fin变窄的时候,你的能带隙会提升,然后你的阈值电压就会发生漂移”,Chudzik说。

这就是为什么芯片制造商对GAA产生兴趣,GAA比我们现在做的所有东西都要复杂,但对于FinFet来说,这是一个自然进化。Lam Research.的CTO和高级VP Dave Hemker表示。

从表面上看,GAA和栅极夹杂在源极和漏极之间的MOSFET很类似。另外,GAA 同样包含了Finfet,但和目前fin是垂直使用的Finfet不同,GAA的Finfet是在旁边。

GAA Fet包含了三个或者更多的纳米线,形成沟道的纳米线悬空且从源极跨到漏极。其尺寸是惊人的。IMEC最近介绍的一个GAA fet的纳米线只有8nm直径。

控制电流流动的HKMG架构能够填补源极和漏极之间的差距。

于是,问题已经很清晰了,我们为什么需要GAA。

“实际上,我认为在其在静电学上面的性能是不够优越的”,应用材料的Chudzid表示。你对GAA抱有期望是因为其可变性以及其可变的性能。

Coventor的CTO DavidFried也认同这个观点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)