本文介绍了一种基于FPGA的用于高分辨率视频图像处理的SDRAM控制器的设计方法。通过设置SDRAM的工作状态,使其工作在猝发模式。在视频时序信号控制下,用多行连续的SDRAM存储空间,存取视频数据。并在数据接口部分增加FIFO,缓存一行视频,在像素时钟控制下,实现视频数据实时的存储和读取。通过改变相关参数,能对所有VESA分辨率视频流进行 *** 作。具有通用性强、系统复杂度低、可靠性高、可扩展等特点。在某型号的机载大屏显示器系统中,用该SDRAM控制器实现了图像的翻转等功能,也验证了该控制器的实用性。

0引言

随着人们对视频图像的清晰度和细节显示要求的不断提高,高分辨率、高bit位的视频标准相继被推出。

造成了数据处理速度和数据处理量极大的增加,也给数据缓存的容量和控制提出较高的要求。在常用的存储器中,SDRAM具有大容量和高速度的特点,并且价格也比较便宜,在视频图像处理中被广泛的用于图像缓存。在基于FPGA的高分辨率视频图像处理系统中,不可避免地会涉及到用FPGA实现SDRAM控制器的方法。但由于SDRAM的 *** 作方式较复杂,常见的控制器支持的视频分辨率普遍都不高。在高分辨率的视频图像已经普及的今天,支持高分辨率的SDRAM控制器的设计也已经被越来越多的视频图像处理人士关注。本文介绍的这种控制器,采用的是Micron公司的MT48LC4M32B2TG(1M×32×4 banks)SDR SDRAM,在Altera的StraTIxⅡ系列FPGA EP2S60F1020I4上进行的开发。

在此平台上采用VHDL语言开发了SDRAM的控制器。

该控制器实现了最高分辨率为1 600×1 200@60 Hz的视频流的缓存和图像翻转的功能。

1 SDRAM基本 *** 作

SDRAM主要包括初始化、读/写 *** 作、刷新、激活、预充电等 *** 作。以MICRON公司的MT48LC4M32B2TG型号SDRAM为例分别介绍。

1.1初始化

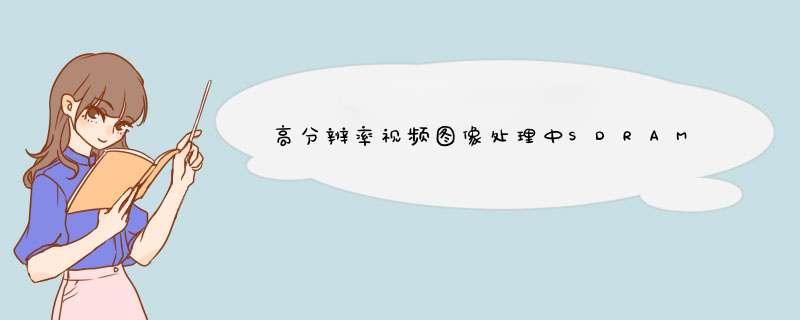

SDRAM在上电后必须执行初始化 *** 作,主要流程为:首先在电源电压和时钟稳定后,经过100μs的延时,执行一次空 *** 作;然后进行预充电 *** 作,使所有 BANK都进入空闲状态;再然后执行两个自动刷新命令;执行完自动刷新后进入模式设置状态,通过地址总线A[11:0]发送数据来设置模式寄存器。模式寄存器设置定义如图1所示。

1.2读/写 *** 作

首先激活具体的BANK和行;然后发出读或写命令,和所要访问的起始列。在读命令发出后,要等待CAS延迟时间,有效数据才会出现在数据总线上。在写命令发出后,有效数据立即出现在数据总线上。读写命令可分为单个模式和猝发模式,猝发模式根据猝发长度分为1,2,4,8和全页模式。猝发 *** 作可用猝发终止命令(BURST TERMINATE)结束。

1.3刷新

由于SDRAM的内部电路特点,必须执行刷新命令,以防止数据丢失。要求64 ms内至少刷新4 096次。

1.4激活

在读/写命令之前都要发出激活命令,激活特定BANK中的某一行。激活后此行一直处于有效状态,直到接收到预充电命令。

1.5预充电

预充电命令用于关闭特定BANK中的某一行,或者所有BANK.

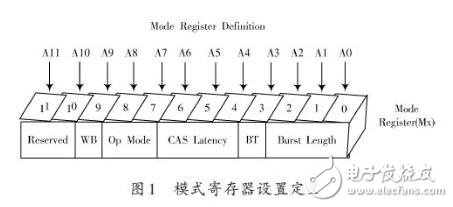

各种 *** 作命令对应的SDRAM管脚电平状态如表1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)