LTE(Long Term EvoluTIon)是“准4G”的技术,以OFDM/FDMA和MIMO为其核心技术。它对实时业务、高可靠性业务和广播级多播业务都能提供较好的支持。LTE在20 MHz频谱带宽下能够提供下行100 Mb/s和上行50 Mb/s的峰值速率,高速率对信道编码和译码技术提出了更高的要求。

对于LTE低时延、高速率和高可靠性的要求,降低译码的实现复杂度和时延以及提高其可靠性对LTE系统性能就显得极其重要,也是一个巨大的挑战。

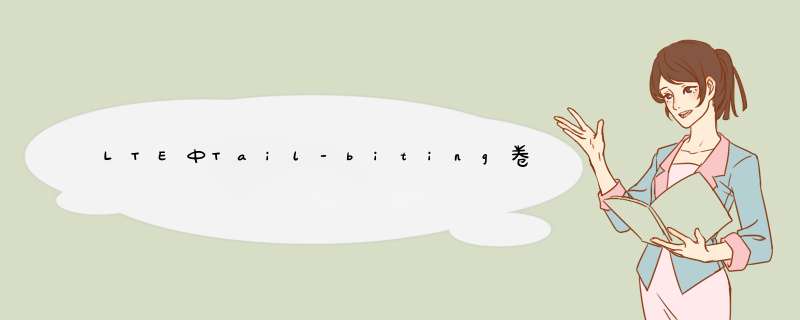

1 LTE中Tail-biTIng卷积码

卷积码通常用(n,k,N)表示。其中k表示输入编码器的数据位数;n表示编码器输出的数据位数;N为编码约束长度,R=k/n是卷积码的码率。

LTE中使用的Tail-biTIng卷积码编码器结构如图1所示。其约束长度N=7,码率R=1/3。

编码器移位寄存器的初始状态值被设置为相应的输入数据流的最后6个信息比特,以至于移位寄存器的初始状态和结束状态相同。

图1中,D6D5D4D3D2D1表示编码器的状态索引(State Index);ck表示输入数据比特;

表示输出数据比特。

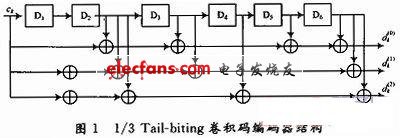

卷积码网格图中的蝶形结构,如图2所示。

随着编码比特的输入,编码器状态的转移过程,由图2可以看出,时刻t-1的两个相关状态Si和Sj转移到时刻t的两个状态Sm和Sn。图中,PM和BM分别表示路径度量和分支度量,其中BM的下标为输出比特

的组合。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)