关键词:非易失性存储器, 数字信号处理器, 串行外设接口

数字信号处理器(DSP)的应用日趋广泛,而重要数据的非易失性保存问题常常是DSP应用中不可缺少的一部分。目前,非易失性的数据保存方法多采用EEPROM(电可擦可编程只读存储器)芯片。本文介绍的X5165芯片,可以较好地完成非易失性数据的保存问题。

在某型号交流伺服系统中,要求能够随时对各种参数设置进行非易失性保存。考虑到具有串行外设接口(Serial Peripheral Interface,SPI)的芯片使用简单,占用PCB板面积小等优点,故,采用了XICOR公司生产的16kbit SPI EEPROM芯片来存储重要数据。

1 TMS320LF2407A的串行外设接口简介

TMS320LF2407A是TI公司开发生产的16位定点DSP。TMS320LF2407A采用CMOS工艺制造,工作频率为40MHz,指令周期为25ns。其片内集成了丰富的资源,支持在线编程,非常便于开发设计,且价格低廉,已经进入了传统单片机所占据的领域。

TMS320LF2407A的SPI接口有以下特点:?

(1)4个外部引脚:SPISOMI(SPI从动输出/主动输入引脚),SPISIMO(SPI从动输入/主动输出引脚),SPISTE(SPI从动发送使能引脚),SPICLK(SPI串行时钟引脚)。?

(2)发送和接收 *** 作可通过中断或查询方法来完成。?

(3)可编程波特率,当频率为40MHz时,波特率可达10Mbps。?

(4)数据字长:1~16个数据位。?

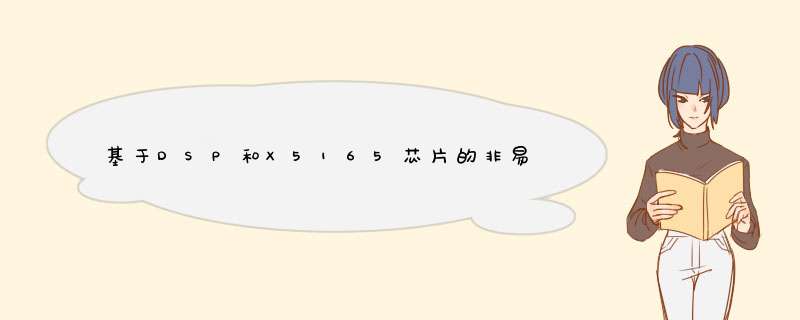

(5)4种时钟方案(由时钟极性和时钟相位控制),如图1所示。四种不同的时钟方式如下:

·无延时的下降沿:串行外设接口在SPICLK信号下降沿发送数据,在SPICLK信号上升沿接收数据;?

·有延时的下降沿:串行外设接口在SPICLK信号下降沿之前的半个周期时发送数据,在SPICLK信号下降沿接收数据;?

·无延时的上升沿:串行外设接口在SPICLK信号上升沿发送数据,在SPICLK信号下降沿接收数据;?

·有延时的上升沿:串行外设接口在SPICLK信号上升沿之前的半个周期时发送数据,在SPICLK信号上升沿接收数据。?

(6) 同时接收和发送 *** 作。?

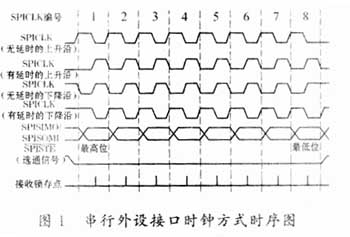

2 硬件连接电路?

X5165的主要特点如下:(1)可编程的看门狗定时器;(2)工作电压管理,并产生复位信号;(3)SPI接口,波特率可达2Mbps;(4)数据块锁定功能和片内偶然性的写保护功能等。

TMS320LF2407A能与多片不同种类的带SPI接口的芯片相连。本文给出了该芯片与X5165的硬件连接,如图2所示。通过SPISIMO引脚发送数据,SPISOMI引脚接收数据,SPICLK引脚发送时钟信号。两个IO引脚IOPB4、IOPB5用来控制 (写保护)和片选信号。?

(写保护)和片选信号。?

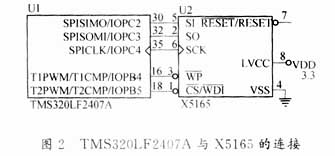

3 X5165的工作原理

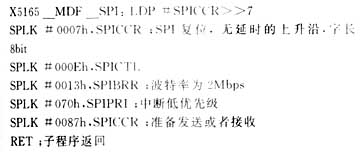

X5165包含了一个8位的指令寄存器。SI引脚上输入的数据在SCK上升沿被锁存,片内的数据在SCK下降沿输出到SO引脚上。所有的指令、地址和数据都是先传输最高位,指令、数据为8位,地址为16位。时钟SCK允许 *** 作过程中停止并在其后恢复。根据图1所示,应该选用“无延时的上升沿”这一时钟方式,且数据字长为8位。X5165的指令集如表1所示。

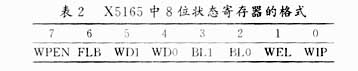

X5165包括一个8位状态寄存器,格式如表2所示。?

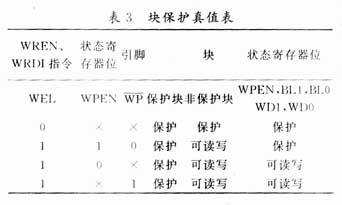

表2中,WIP位是指出非易失性写 *** 作是否忙,只读位,为1,写 *** 作正在进行,为0,无写 *** 作。WEL是写使能锁存状态位,它可以用WREN指令置位,用WRDI指令复位。WPEN与 引脚组合,实现保护存储阵列和状态寄存器位WPEN、BL1、BL0、WD1、WD0,是非易失性位,可用WRSR指令对WPEN位编程。其组合如表3所示。

引脚组合,实现保护存储阵列和状态寄存器位WPEN、BL1、BL0、WD1、WD0,是非易失性位,可用WRSR指令对WPEN位编程。其组合如表3所示。

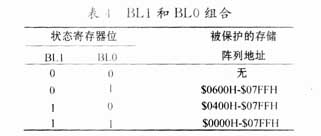

BL1、BL0是存储器块保护位,为非易失性位。其组合可通过WRSR指令编程,可以保护存储器阵列范围,如表4所示。

选定保护的块,用户只能读不能写。

WD1、WD0是看门狗定时器位,为非易失性位,可用WRSR指令进行编程。

在读状态寄存器时,先将片选信号拉到低电平,然后通过SPI接口发送数据,先发送RDSR指令,接着提供8个SCK脉冲,就可以将寄存器的内容读回到TMS320LF2407A中。

在写状态寄存器时,参考表3,可知,必须先用WREN指令将WEL位置位。由于本文提供的电路能控制 引脚,故,直接将该引脚电平拉为高电平,就可以对状态寄存器进行写 *** 作。在写状态寄存器时,先将片选信号拉到低电平,然后发送数据,先发送WRSR指令,然后发送8位待写入的内容。注意,状态寄存器的只读位不受影响。

引脚,故,直接将该引脚电平拉为高电平,就可以对状态寄存器进行写 *** 作。在写状态寄存器时,先将片选信号拉到低电平,然后发送数据,先发送WRSR指令,然后发送8位待写入的内容。注意,状态寄存器的只读位不受影响。

在读存储阵列时,先将片选信号拉到低电平,然后通过SPI接口发送数据,先发送READ指令,接着发送16位地址,选定的存储单元中的数据在SCK下降沿读回TMS320LF2407A中。每个数据被送出后,芯片内的地址计数器自动加1,继续提供SCK脉冲,可读出下一个存储单元的数据。当地址计数器达到$07FFH时,自动翻转到$0000H单元。读数据完成后,将片选信号拉到高电平。

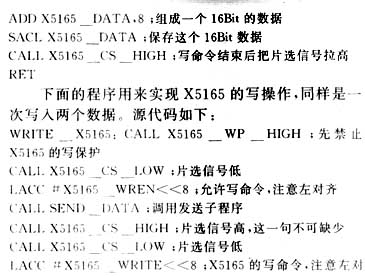

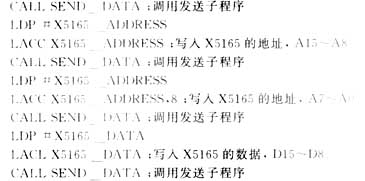

在写 *** 作进行之前,参考表3,可知必须置位“WEL”。然后,需要将非保护块设置为可读写方式。根据图2表示的连接,可知,只需要将 引脚电平拉高,就可以进行写 *** 作。当然也可以通过对WPEN位进行编程实现。在写存储阵列时,先将片选信号拉到低电平,接着通过SPI接口发送数据,先发送WRITE指令,然后发送16位地址,接着发送8位的数据。每个数据被送出后,芯片内的地址计数器自动加1,继续提供SCK脉冲,可继续将数据写入下一个存储单元。当地址计数器达到$07FFH时,自动翻转到$0000H单元。写数据完成后,将片选信号拉到高电平。值得注意的是,每次写 *** 作完成后,都必须查询WIP位来确定写 *** 作是否完成,否则,如果连续进行两次写 *** 作,可能会出错。

引脚电平拉高,就可以进行写 *** 作。当然也可以通过对WPEN位进行编程实现。在写存储阵列时,先将片选信号拉到低电平,接着通过SPI接口发送数据,先发送WRITE指令,然后发送16位地址,接着发送8位的数据。每个数据被送出后,芯片内的地址计数器自动加1,继续提供SCK脉冲,可继续将数据写入下一个存储单元。当地址计数器达到$07FFH时,自动翻转到$0000H单元。写数据完成后,将片选信号拉到高电平。值得注意的是,每次写 *** 作完成后,都必须查询WIP位来确定写 *** 作是否完成,否则,如果连续进行两次写 *** 作,可能会出错。

4 X5165相关 *** 作的软件实现

TMS320LF2407A的串行外设接口模块很容易实现对X5165的各种 *** 作,且由于该DSP具有非常丰富的片内资源,因此,使用了两个IO引脚控制 信号和片选信号。

信号和片选信号。

首先是TMS320LF2407A的SPI模块初始化工作。本文给出实际使用的源代码如下:

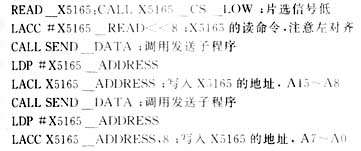

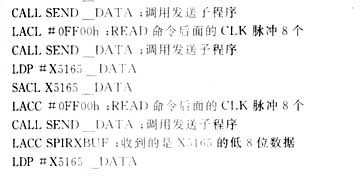

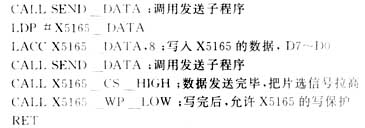

下面的程序用来实现X5165的读 *** 作。因为TMS320LF2407A是16位机,故,一次读写两个8位数据。源代码如下:

下面是发送子程序,寄存器ACC载入待发送的数据,读回的数据也返回到ACC中,源代码如下:

SEND——DATA:LDP #SPITXBUF>>7?

SACL SPITXBUF;待发送的数据?

LDP #SPISTS>>7?

S——5165: BIT SPISTS,BIT6 ;检测SPI——INT位?

BCND S——X5165,NTC ;如果SPI——INT为0,继续查询?

LACC SPIRXBUF;读回数据,保存在ACC中?

RETP?

限于篇幅,TMS320LF2407A对X5165的其他软件 *** 作不再赘述。按照上面的硬件、软件的设计思想,已经将X5165成功地应用于某型号的交流伺服系统中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)