关键词:FPGA,同步,测距

1 引 言

现场可编程门阵列(FPGA)用硬件电路完成算法的过程,一方面解决了系统的开销问题,提供了提高系统整体性能的条件,另一方面,由于静态RAM型的FPGA具备可重构特性,这使得资源利用率得到显著提高。FPGA既具有通用计算系统的灵活性,又有专用处理系统的性能,对实现高性能信号处理具有很高的应用价值,而且可重构的特性使其可以根据算法来调整相应的通信结构和数据字长。FPGA以其高度的灵活性与硬件的高密度性在通信信号处理中得到了广泛的应用。

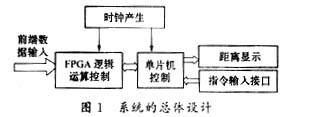

在对Xilinx公司的Virtex-E系列FPGA芯片进行充分理解的基础上,结合炮兵某数字测距定位系统的实现,这里设计了伪码的测距电路,并对其FPGA的实现进行了分析。

系统伪码测距电路总体设计如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)